# **Transistors**

From Crystals to Integrated Circuits

M. Levinshtein and G. Simin

**World Scientific**

# This Page Intentionally Left Blank

# TRANSISTORS FROM CRYSTALS TO INTEGRATED CIRCUITS

# M Levinshtein & G Simin

IOFFE Institute of Russian Academy of Sciences, Russia

Translated by

# Minna M Perelman

Published by

World Scientific Publishing Co. Pte. Ltd. P 0 Box 128, Farrer Road, Singapore 912805

USA office: Suite 1B, 1060 Main Street, River Edge, NJ 07661

UK office: 57 Shelton Street, Covent Garden, London WC2H 9HE

#### British Library Cataloguing-in-Publication Data

A catalogue record for this book is available from the British Library.

#### TRANSISTORS, FROM CRYSTALS TO INTEGRATED CIRCUITS

Copyright © 1998 by World Scientific Publishing Co. Pte. Ltd.

All rights reserved. This book, or parts thereof, may not be reproduced in any form or by any means, electronic or mechanical, including photocopying, recording or any information storage and retrieval system now known or to be invented, without written permission from the Publisher.

For photocopying of material in this volume, please pay a copying fee through the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, USA. In this case permission to photocopy is not required from the publisher.

ISBN 981-02-2743-4

This book is printed on acid-free paper.

Printed in Singapore by Uto-Print

To my friends. M.L. To my sons Kirill and Misha. G.S.

# This Page Intentionally Left Blank

## **Preface**

This book will tell you about the design and work of transistors and diodes—the most important semiconductor devices.

A few years ago this book was published in Russian in Moscow and about 140 000 copies of it were sold in the former USSR.

We found that the majority of those who had bought it were senior grade pupils interested in semiconductors, those who thought about their future careers, those who were considering semiconductor physics, materials science, electrical engineering or semiconductor processing as their future profession, though they didn't quite realize what semiconductor electronics actually is.

Many of our readers were undergraduates (mainly freshmen). We were glad to know that the book had proved to be useful supplementary reading, facilitating their learning process.

We did not expect it and were happy to know that graduates and postgraduates were also interested in the book. Some of our readers have degrees (B.Sc., or M.Sc., some are getting PhDs), and yet they wrote to tell us that what had seemed to them most complicated and perceivable only by means of differential equations and computer simulation, became quite simple and understandable after they had read the book. Semiconductor designers and technologists were also interested in the book. They found some new ideas and unexpected approaches in the book.

Several professors, who deliver lectures in semiconductor physics and semiconductor devices, have written to us saying that they think it is expedient to recommend the book to their students as supplementary reading.

Thus, the book has proved to be interesting to quite a lot of people whose range and levels of knowledge are very different.

We are thankful to our friends and colleagues: Michael I. Dyakonov, Professor, Principal Scientist of the Ioffe Institute, St. Petersburg, Russia; Boris I. Shklovskii, Professor, University of Minnesota, USA; Igor M. Filanovskii, Professor, University of Alberta, Canada for their help in the work featured in this book. We are grateful to our wives Larisa and Marianna for their

patience, understanding and friendly support. We want to thank our children: Dina Levinshtein and Misha and Kirill Simin for their love which helped a lot. We are grateful to Minna M. Perelman, the translator of this book, and also of our book "Getting to Know Semiconductors", published by World Scientific in 1992. Her energy and courage inspired our work. Our special thanks are also extended to Marianna A. Simin: her funny pictures created an easy and friendly atmosphere.

M. Levinshtein G. Simin

# Contents

| Preface                                                                                                                                                                                                  | vii |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Introduction                                                                                                                                                                                             | 1   |

| Introduction  Part I. Semiconductors  Chapter 1. The Main Properties of Semiconductors  1.1 Intrinsic Semiconductors  1.1.1 "Free electrons" in crystal  1.1.2 Holes  1.1.3 Generation and recombination | 3   |

| Chapter 1. The Main Properties of Semiconductors                                                                                                                                                         | 7   |

| 1.1 Intrinsic Semiconductors                                                                                                                                                                             | 7   |

| 1.1.1 "Free electrons" in crystal                                                                                                                                                                        | 8   |

| 1.1.2 Holes                                                                                                                                                                                              | 9   |

| 1.1.3 Generation and recombination                                                                                                                                                                       | 10  |

| Thermal generation                                                                                                                                                                                       | 11  |

| Electron-hole recombination                                                                                                                                                                              | 12  |

| Intrinsic concentration                                                                                                                                                                                  | 13  |

| The simplest band diagrams                                                                                                                                                                               | 14  |

| 1.2 Impurity Semiconductors                                                                                                                                                                              | 16  |

| 1.2.1 Donor impurity                                                                                                                                                                                     | 17  |

| 1.2.2 Acceptor impurity                                                                                                                                                                                  | 19  |

| 1.2.3 The temperature dependence of the carrier concentration                                                                                                                                            | 21  |

| 1.2.4 Minority carriers                                                                                                                                                                                  | 23  |

| 1.2.5 Band diagrams                                                                                                                                                                                      | 24  |

| Compensation                                                                                                                                                                                             | 26  |

| 1.3 Deep Levels                                                                                                                                                                                          | 28  |

|                                                                                                                                                                                                          | 29  |

| 1.3.2 Generation through deep levels                                                                                                                                                                     | 31  |

| 1.3.3 Recombination through deep levels                                                                                                                                                                  | 34  |

| 1.4 Summary                                                                                                                                                                                              | 36  |

| Chapter 2. Motion of Electrons and Holes inside the Crystal                                                                                                                                              | 39  |

| 2.1 Thermal Motion                                                                                                                                                                                       | 40  |

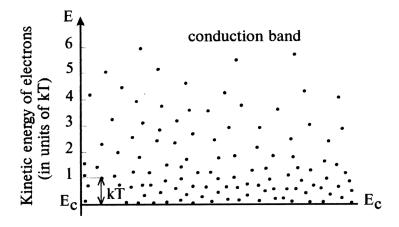

| 2.1.1 Energy distribution of electrons                                                                                                                                                                   | 40  |

| 2.1.2 Energy distribution of holes                                                                                                                                                                       | 42  |

| 2.2 Motion in the Electric Field                                              | 48  |

|-------------------------------------------------------------------------------|-----|

| 2.2.1 "Hot" electrons                                                         | 50  |

| 2.2.2 Band diagrams                                                           | 51  |

| 2.3 Diffusion                                                                 | 55  |

| 2.3.1 Diffusion coefficient                                                   | 57  |

| 2.3.2 Diffusion current                                                       | 59  |

| 2.3.3 Diffusion length                                                        | 60  |

| 2.4 Summary                                                                   | 64  |

| Part II. Barriers & Junctions                                                 | 65  |

| Chapter 3. The Barrier on the Crystal Boundary                                | 67  |

| 3.1 Work Function                                                             | 69  |

| 3.1.1 Come back, return, I call you back!                                     | 70  |

| 3.1.2 Double charged (dipole) layer                                           | 70  |

| 3.1.3 How to define the work function                                         | 72  |

| Red boundary of the extrinsic photoelectric effect                            | 72  |

| Thermoionic emission                                                          | 73  |

| 3.1.4 What work function is equal to                                          | 74  |

| Work function in metals                                                       | 74  |

| Work function in semiconductors                                               | 74  |

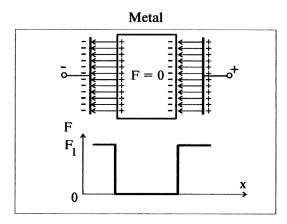

| 3.2 Surface States                                                            | 78  |

| 3.3 Bending Bands, Surface Potential                                          | 80  |

| 3.4 Summary                                                                   | 84  |

| Chapter 4. The Main Parameters of Potential Barriers                          | 85  |

| $4.1~\mathrm{How}$ the Electric Field Penetrates into a Metal, Dielectric and |     |

| Semiconductor                                                                 | 86  |

| 4.1.1 Why the electric field practically does not penetrate into a            |     |

| metal                                                                         | 86  |

| 4.1.2 How the electric field penetrates into a dielectric                     | 88  |

| 4.1.3 In what way and how deep the electric field penetrates into             | 0.0 |

| a semiconductor                                                               | 90  |

| 4.2 Field Dependence on the Coordinate                                        | 92  |

| 4.3 Poisson's Equation                                                        | 94  |

| 4.4 A Few Words about Accumulation Layers                                     | 97  |

| 4.5 Summary                                                                   | 98  |

| Chapter 5. p-n Junction                                     | 99  |

|-------------------------------------------------------------|-----|

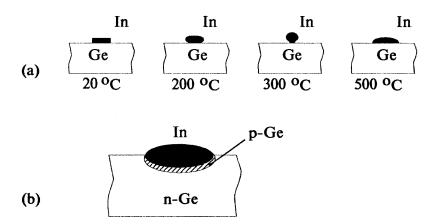

| 5.1 Ways of Obtaining $p$ - $n$ Junctions                   | 99  |

| 5.1.1 Alloying                                              | 101 |

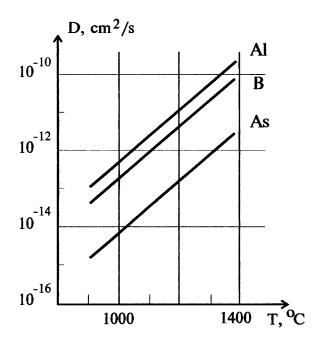

| 5.1.2 Diffusion                                             | 103 |

| 5.1.3 Ion implantation                                      | 105 |

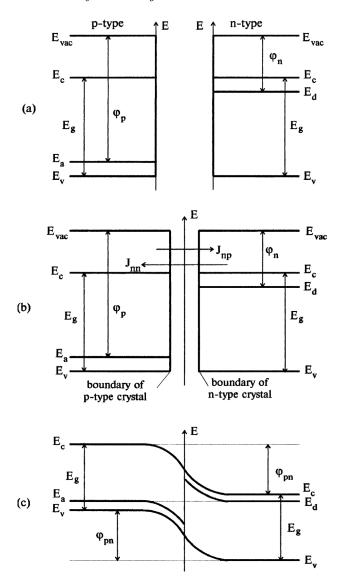

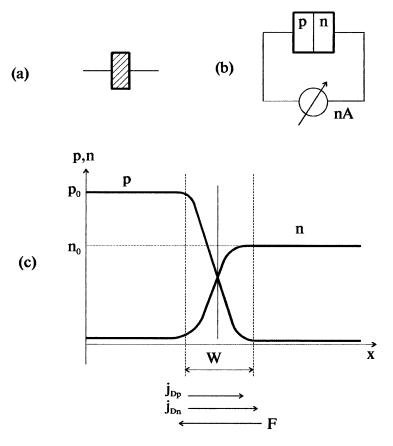

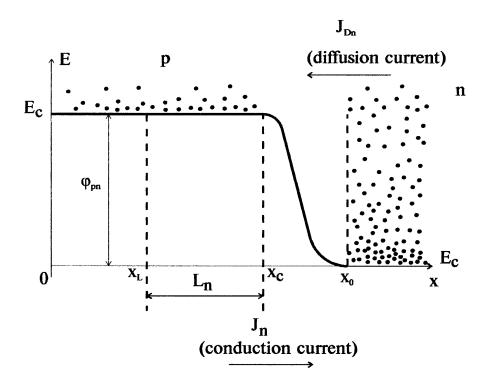

| 5.2 Barrier on the Boundary                                 | 108 |

| 5.2.1 The height of the barrier                             | 111 |

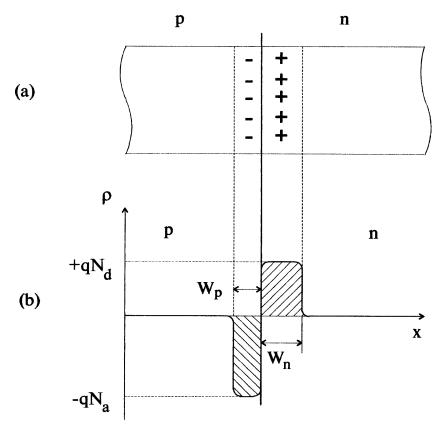

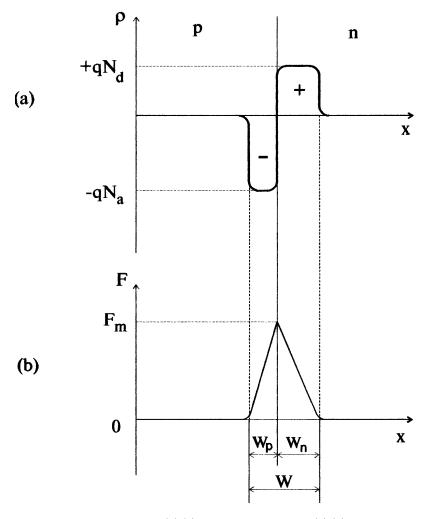

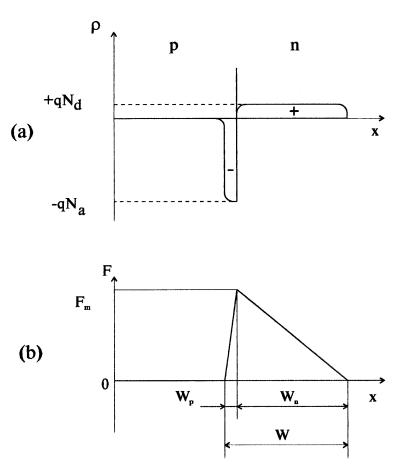

| 5.2.2 Depletion layer. Width of the barrier                 | 113 |

| 5.2.3 Wonderful equilibrium                                 | 117 |

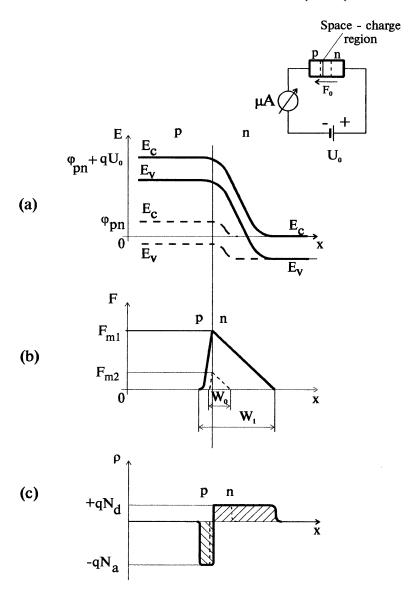

| 5.2.4 The reverse bias                                      | 124 |

| Height and shape of the barrier                             | 126 |

| Reverse current                                             | 127 |

| Barrier capacity                                            | 130 |

| 5.2.5 The forward bias                                      | 133 |

| The height of the barrier                                   | 133 |

| Forward current                                             | 133 |

| Injection                                                   | 137 |

| 5.3 Summary                                                 | 143 |

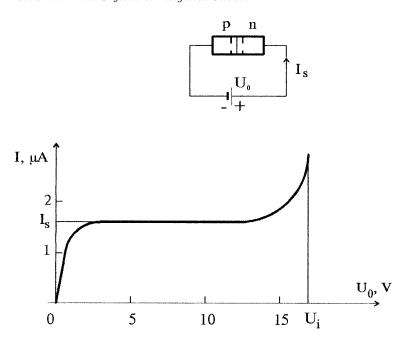

| Chapter 6. Diodes with the $p$ - $n$ Junctions              | 145 |

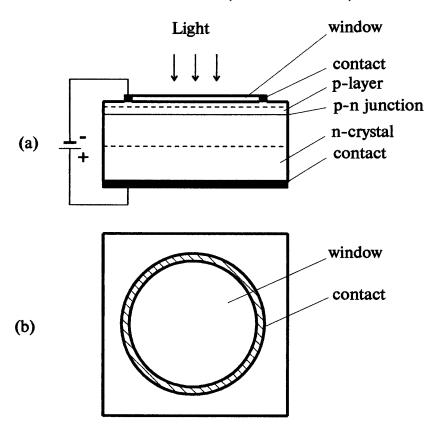

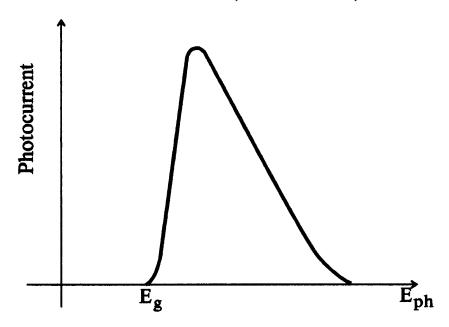

| 6.1 Photodiodes                                             | 145 |

| 6.2 Variable Capacitors                                     | 149 |

| 6.3 Light-Emitted Diodes                                    | 151 |

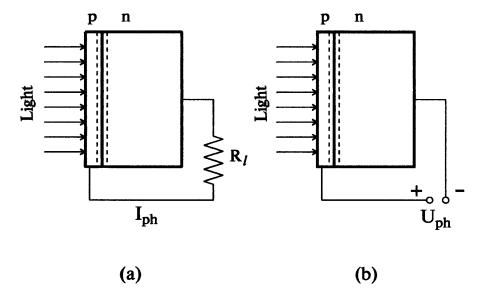

| 6.4 Solar Cells                                             | 154 |

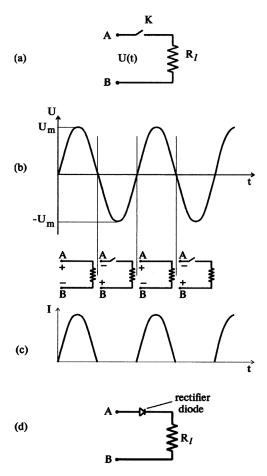

| 6.5 Rectifier Diodes                                        | 159 |

| 6.6 Summary                                                 | 165 |

| Part III. Transistors                                       | 167 |

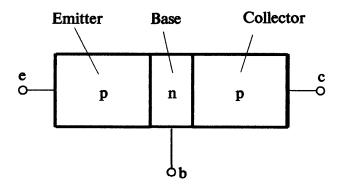

| Chapter 7. Bipolar Transistors                              | 169 |

| 7.1 Principle of Operation of a Bipolar Transistor          | 170 |

| 7.1.1 Current amplification                                 | 172 |

| 7.1.2 Parable about what is main and what is minute         | 175 |

| 7.1.3 Speed of response of the transistor                   | 176 |

| 7.2 Some Words about the Types and Manufacturing of Bipolar |     |

| Transistors                                                 | 185 |

| 7.3 The Simplest Transistor Circuits              | 191 |

|---------------------------------------------------|-----|

| 7.4 Summary                                       | 197 |

| Chapter 8. Field Effect Transistors               | 199 |

| 8.1 The Beginning                                 | 199 |

| 8.1.1 The main idea                               | 199 |

| 8.1.2 Simple estimations                          | 201 |

| 8.1.3 Old acquaintances                           | 202 |

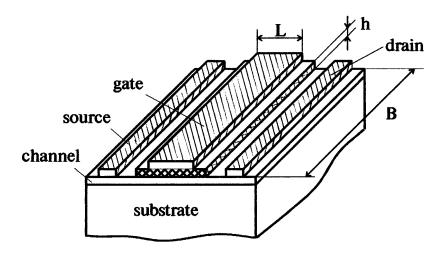

| 8.2 Maturity and Flourishing                      | 203 |

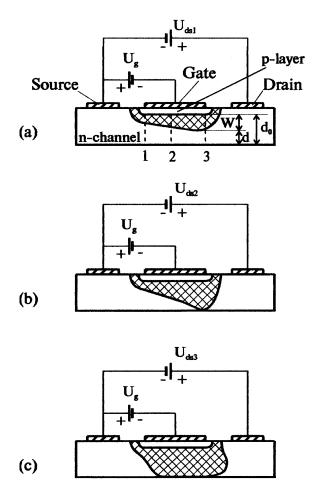

| 8.2.1 JFET (p-n-junction field effect transistor) | 203 |

| 8.2.2 Fortune favours the brave. MOSFET           | 205 |

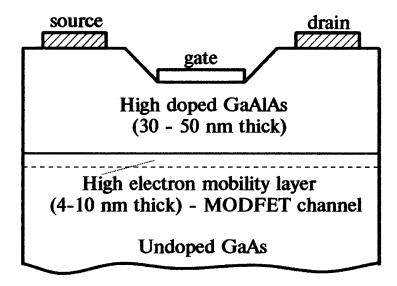

| 8.3 Epitaxy                                       | 209 |

| 8.4 A Few Important Details                       | 211 |

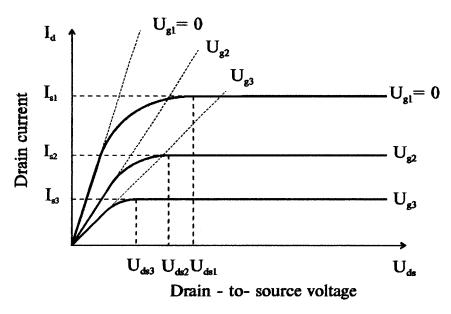

| 8.5 The Work of the FETs in Actual Regimes        | 213 |

| 8.5.1 The main parameters of FETs                 | 217 |

| Transconductance                                  | 217 |

| Speed of response                                 | 220 |

| 8.6 FET as an Element of Electronic Circuits      | 222 |

| 8.7 Summary                                       | 223 |

| Chapter 9. Transistors and Life                   | 225 |

| 9.1 The First King                                | 226 |

| 9.2 Ugly Duckling                                 | 228 |

| 9.3 Long Live the New King!                       | 231 |

| 9.4 The King Disappears. Long Live the New King!  | 233 |

| 9.5 Claimants to the Throne                       | 239 |

| Three-dimensional intergrated circuits            | 239 |

| Semiconductor elements of the optical computers   | 240 |

| Bioelectronics                                    | 240 |

| Conclusion                                        | 241 |

## Introduction

Where there is a will, there is a way.

It's a long way to Tipperary, It's a long way to go, It's a long way to little Mary, To the sweetest girl I know...

Semiconductor devices are numerous, even the most important of them make dozens, with each of them, as a rule, having lots of species.

In the library you can see a great many reference books, hundreds of pages each. Those reference books mention only the main properties of the most widely used semiconductor devices. But they do not say anything of the physical principles of the work of those devices.

Those principles are given in other thick volumes, again hundreds of pages each. Finally, there are many very thick books describing the application of semiconductor devices. How is one to orientate himself among those numerous devices and principles?

The point is that the work of a great many devices is based on a rather limited number of ideas. Some of those are quite simple and evident, others require certain effort and patience. After you have perceived those ideas and principles, you can understand the design and principle of operation of practically any semiconductor device.

First, in Part I of this book, Semiconductors, we will get to know the main properties of semiconductors. It is most essential to know them in order to understand the work of any semiconductor device. Some devices are based on a remarkable property of semiconductors — their ability to change their electric resistance even at the slightest alteration of the environmental conditions. Therefore, measuring the resistance of semiconductors, one can measure the temperature and illumination, pressure and magnetic field, the

#### 2 Introduction

electric field and the velocity of the motion of liquid or gas, the acceleration or the extent of smoke-screen in the premises. Such devices are widely used in households and industry, in scientific research and the military service. Millions and millions of such devices are produced every year.

The main properties of semiconductors and the work of the devices, based on those properties, have been discussed in detail in our book "Getting to Know Semiconductors". However, even if you have read that book, we recommend you not to skip the first part of this book. This is because we widely use a simple and expressive technique here — the "language" of energy diagrams. That "language" was not employed when describing the most simple semiconductor devices, but it proved most useful when describing the work of diodes and transistors. The basis of that language is introduced in Part I of this book. However, in order to understand the principle of diodes and transistors, it is not enough just to know the properties of semiconductors. It is also quite essential to study very interesting, unusual and not very simple phenomena — the so-called *junctions*. It may be *homojunction*, a region inside the semiconductor, whose different parts are doped with different impurities; it may be heterojunction, a region emerging on the border between two different semiconductors. In the vicinity of those borders there appear regions with quite peculiar properties — energy barriers, which determine the work of diodes and transistors.

The properties of junctions will be discussed in Part II of this book. And here we will discuss various types of diodes.

The third part of this book is devoted to the principle of design, work and application of transistors.

<sup>&</sup>lt;sup>1</sup>M. E. Levinshtein, G. S. Simin. Getting to Know Semiconductors. World Scientific. Singapore — New Jersey — London — Hong-Kong, 1992. ISBN 981-02-0760-3.

## Part I

# Semiconductors

"The English physicist Cavendish has proved experimentally that water conducts electricity 400 million times worse than metals; nevertheless it is not a very bad conductor of electricity. Bodies which take the intermediate position between conductors and nonconductors are usually called SEMICONDUCTORS" Ivan Dvigubsky.

"Fundamentals of Experimental Physics", 1826

There is such a striking variation in the conductivity of different substances that one can't help but be surprised at it. The conductivity of a good conductor, like silver, is about  $10^{22}$  times greater than the conductivity of a good insulator, like glass. To better understand the difference between the conductivity of good metals and that of good insulators, one should realize that it is the same as the difference between the diameter of our galaxy and the length of 1 cm!

Though the atoms of any substance are electrically neutral, any atom, silver, copper, nitrogen, oxygen, germanium or silicon contains the same number of positively charged protons and negatively charged electrons. So, on the whole, every atom is neutral. The volume, filled with neutral particles, is incapable of conducting the electric current. Consequently, the volume filled with separate isolated atoms of any substance — silver, silicon or diamond — is in fact an ideal insulator.

But why do those substances, when they are in the solid state, have quite different conductivities? Solids seem to be composed of the same atoms.

Moreover, the atoms of one and the same substance, e.g. of carbon (C), depending on the type of crystal they form, can be either a very good conductor (graphite), or a perfect insulator (diamond).

The last example suggests that whether the solid is a metal or a dielectric depends not so much on the properties of the atoms forming the crystal, as on the types of the bonds of atoms in the crystal lattice of the solid body.

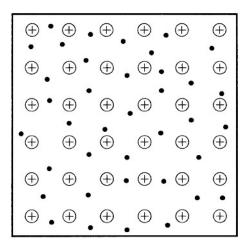

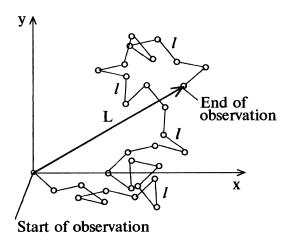

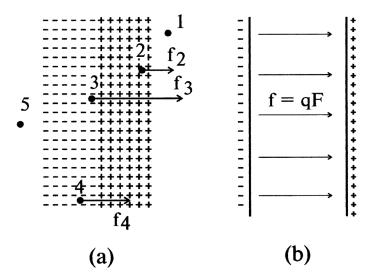

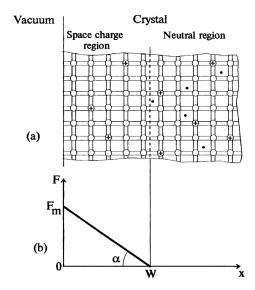

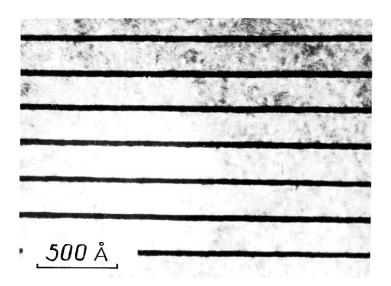

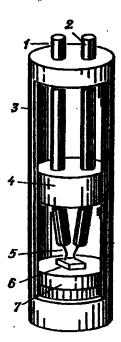

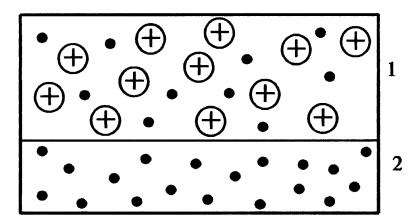

Figure 1 and 2 demonstrate two main types of crystal lattice. Figure 1 illustrates the main properties of metallic crystals. The crystal lattice is formed by positively charged ions, not by neutral atoms. While forming the lattice, each atom loses one valence electron, and these electrons (shown as black circles in Fig. 1) do not belong then to any specific ion of the metal. These electrons are said to be collectivized by the crystal and can move freely under the action of the external electric field. There are  $\sim 10^{22}$  free carriers — electrons — in every cubic centimetre of the metal. It is no wonder that metals are perfect conductors.

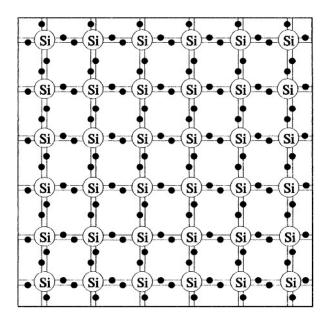

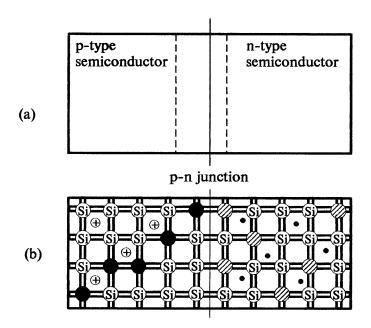

The scheme of the crystal lattice of silicon, shown in Fig. 2, demonstrates another type of bond in a crystal. Every atom is linked with the neighbouring atoms by means of strong electron bonds.

Fig. 1. Schematic diagram of the metal crystal lattice. The regular lattice of positively charged ions is plunged into the "gas" of free electrons, having no tight bonds with separate ions.

Fig. 2. Schematic diagram for the silicon (Si) crystal lattic. The lines linking the Si atoms represent electron bonds.

The field which keeps the electrons in their orbits is very strong. By order of magnitude they make  $\sim 10^{10}$  V/m. Therefore it is not easy to break the electron coupling between the atoms and knock out the electron from the orbit. And while all the valent electrons are coupled on the interatomic orbits, there are no free electrons in the crystal i.e. there are no electrons able to move under the action of the external electric field within the crystal. Therefore, the ideal crystal, shown in Fig. 2, will be an ideal dielectric.

But alas, as we know from our own experience, ideal objects in the real world exist only in our imagination. Any defect of the crystal lattice, any foreign impurity, even heat, is able to break the electron bonds shown in Fig. 2 and release some electrons from the interatomic orbits. These released electrons can move under the action of the external electric field. So, in fact, every crystal can conduct electric current. How large that conductivity is depends on the number of released electrons. The latter depends on the fact that it is hard to break the links keeping the electron in the interatomic orbits.

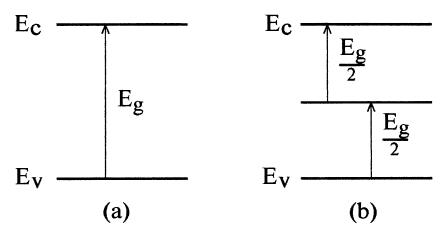

The energy necessary to break the electron bond and free the electron is usually designated by the symbol  $E_q$ . The index "g" comes from the word

"gap." In different non-metallic crystals, the amount of this energy varies from zero to several dozen electronvolts.  $^*$

The value  $E_g$  is one of the most important characteristics of a non-metallic crystal.

If the value  $E_g$  is large, then heating up the crystal even to a very high temperature will hardly create any appreciable number of free electrons. If the value  $E_g$  is large enough, then the crystal melts down before a free carrier is created. Materials with such large values of  $E_g$  are typical dielectrics. A well-known example of a dielectric is common salt, sodium chloride (NaCl). The value  $E_g$  for NaCl is  $\sim 8$  eV.

On the other hand, in metals, where all electrons are free even at the temperature of absolute zero, conductivity is very great. It is clear that crystals with small values of  $E_g$  "take the intermediate position between conductors and nonconductors." Such substances are called *semiconductors*.

Thus, semiconductors are non-metal materials whose energy  $E_g$  is relatively small.

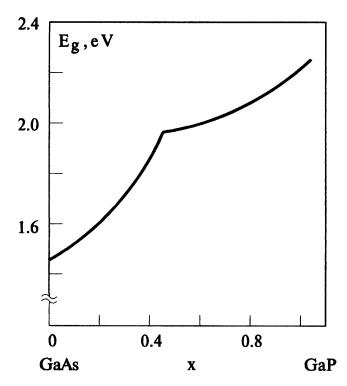

The value  $E_g$  for typical semiconductors varies from a few tenths of an electronvolt up to two or three electronvolts. Thus, for indium antimonide (InSb),  $E_g=0.17\,\mathrm{eV}$ . For germanium (Ge), the material used to make the very first transistors and semiconductor diodes,  $E_g=0.72\,\mathrm{eV}$ . For silicon (Si), which is the main material of the modern semiconductor electronics,  $E_g=1.1\,\mathrm{eV}$ . Gallium arsenide (GaAs), the most promising material for semiconductor electronics of the near future, has  $E_g=1.4\,\mathrm{eV}$ . In the ternary semiconductor compound GaAlAs used to make semiconductor light-emitting diodes and lasers, the value  $E_g$  varies from 1.4 eV (GaAs) to 2.17 eV (AlAs), depending on the relative amount of Al and Ga they contain. Silicon carbide (SiC), the material of the most reliable and stable light-emitting diodes, is able to operate at very high temperatures, has  $E_g\approx 3\,\mathrm{eV}$ .

We have named here only the most important semiconductor materials. But hundreds of semiconductor compounds have been synthesized, studied and made use of.

<sup>\*</sup>A unit of energy of 1 electronvolt (l eV) is equal to  $1.6 \cdot 10^{-19}$  J. The electron acquires the energy of 1 eV after it passes the potential difference of 1 V. When we speak of the properties of solids, it's very convenient to measure the energy in electronvolts. We will frequently use this unit.

# Chapter 1

# The Main Properties of Semiconductors

#### 1.1 Intrinsic Semiconductors

Intrinsic semiconductors are semiconductors in which the concentration of free current carriers is defined only by temperature and by the amount of energy  $E_q$  unique to the given semiconductor.

A logical question can be asked: what else can determine the concentration of free carriers? As we will see further, one of the most characteristic features of semiconductors is their very high sensitivity to a very very small quantity of impurity. A quite negligible (and inappreciable in any other materials) addition of a foreign substance — one atom per million or even milliard of a semiconductor can change its properties to such an extent that the concentration of the free carriers will be determined not by the intrinsic properties of the semiconductor, but by the amount and characteristic of the impurity which was added.

Let us imagine the most simple situation: the semiconductor crystal has no defects and does not contain any impurity. In the ideal crystal lattice, every electron is kept in its orbit, as shown in Fig. 2, and it will take the energy  $E_g$  to release it. The temperature of the crystal is T. What portion of the electron bonds will be broken? Or, how many electrons capable of moving under the action of the field, i.e. conduction electrons, will there be in the crystal?

Chaotic thermal motion tends to break the bonds between the atoms. The value of the energy of thermal motion is known to be kT, where k is the Boltsman constant. The value of  $k=1.38\cdot 10^{-23}$  J/K or  $8.6\cdot 10^{-5}$  eV/K. At room temperature (300 K), the energy of thermal motion  $kT\approx 0.026$  eV. When the temperature is rather high —  $+200^{\circ}$ C or  $\approx 500$  K, the energy kT=0.043 eV. But as we know, the value  $E_g$  for typical semiconductors is much higher. It may seem that in this case the thermal motion will be

incapable of breaking a single electron bond and, provided  $kT \ll E_g$ , there will be no free carriers in the crystal.

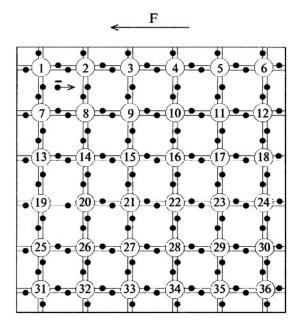

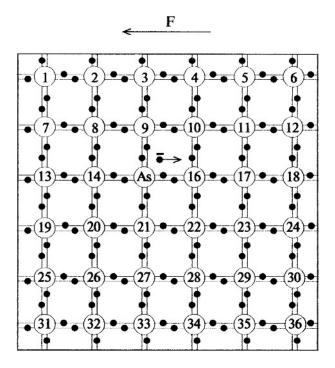

However, the value kT characterizes only the average thermal energy of particles. Due to the chaotic character of thermal motion at any given moment of time, there will be such atoms in the crystal whose energy will prove greater than the value of  $E_g$ . Such atoms will not be numerous. But they will exist, and a part of the electron bonds between the atoms will be broken. What will take place is shown in Fig. 3. One of the links is broken (between atoms 19 and 20). The electron, being dislodged from its orbit, is within the area formed by atoms 1, 2, 7 and 8.

Fig. 3. One of the electron bonds (between atoms 19 and 20) is broken by chaotic thermal motion. A conduction electron appeared (it is located between atoms 1, 2, 7 and 8). The negatively charged electron will move against the electric field F (to the right).

## 1.1.1 "Free electrons" in crystal

From Fig. 3, it is clear that when speaking about an electron dislodged from its orbit, we should preferably use the word "free", at least mentally, in inverted commas.

The electron which is actually free is the one in the vacuum.

The so-called "free" electron in the crystal is in fact in the complex electric fields. The electric fields are formed by the ions of the lattice and by the valence electrons of the neighboring atoms.

Under the action of the external electric field, F, a free electron in the vacuum moves with a constant acceleration  $a = qF/m_0$  (q is the electron charge,  $m_0$  is the mass of the free electron). The "free" electron in a crystal can move freely only for a very short period of time, after which it is sure to collide with the atom of the lattice (Fig. 3). So, when using the term "the free electron in a crystal," we should bear in mind that it denotes in fact just an ability to perform a directed motion under the action of the external electric field, thus conducting an electric current. That is why free electrons in a crystal are called *conduction electrons*.

#### 1.1.2 *Holes*

When the electron bond is broken (Fig. 3), the crystal acquires not one, but two possibilities to conduct the electric current. Let us compare the behaviour of the conduction electron with that of the broken bond (in Fig. 3, it is shown between atoms 19 and 20). If no external field is applied to the crystal, the electron will travel chaotically between the atoms of the lattice under the action of thermal oscillations. And what about the broken bond?

Any of the electrons linking atoms 19 and 20 with the adjacent atoms may get to the trajectory of the dislodged electron and thus restore the broken bond between atoms 19 and 20. If that happened to be the electron which had been linking, say, atoms 14 and 19, then the broken bond will take its position. Then it will be displaced to the position between atoms 9 and 14, or else between atoms 19 and 18. It may also move to the place between atoms 14 and 15. Just like the electron, the broken bond will travel chaotically between the atoms of the lattice.

If the crystal is acted upon by an external electric field, then apart from the chaotic motion, the free electron, as a negatively charged particle, will also acquire a directed motion against the electric field. What about the broken bond? Let us look again at Fig. 3. Now any of the electrons, linking atoms 19 and 20 with the adjacent atoms, can shift to the trajectory between these two atoms (i.e. atoms 19 and 20). However, due to the action of the external field, this shift is most probable for the electrons linking atoms 18 and 19. They would be "pulled" by the external field to the place of the broken bond. The

directed motion along the field will be added to its chaotic motion. However, it does not mean that the broken bond will be necessarily substituted by the electron linking atoms 18 and 19 and that the hole will 1) sure to or 2) indispensably or 3) necessarily appear between atoms 17 and 18. The external electric field does not stop the chaotic motion of the broken bond. It just adds to the chaotic motion some elements of the directed motion. Note that the broken link moves in the direction opposite to that of electron's motion — it moves along the electric field. In other words, it behaves like a positively charged particle.

It goes without saying that the broken link is in fact not a true particle. Unlike the electron, it cannot be extracted from the crystal and studied in the vacuum. However, when discussing the properties of the crystal it is much easier to watch the displacement of a broken bond than the actual displacement of electrons from one orbit to another. A broken bond like this is called a "hole" and it is said to be a quasiparticle.

When a crystal is acted upon by an electric field, then a break in the link, a hole, is an additional source of conductivity. Electrons from the adjacent links jumping from one broken bond to another move against the field and conduct the current. If we are to define this mechanism of conductivity by means of the notion of a hole, we are to consider the hole, traveling in the field in the direction opposite to that of the electrons to be a *positively* charged particle whose charge is equal in magnitude to that of the electron.

Should we expect that the conduction electron and the hole will move with the same velocity in the electric field? Hardly so. Looking at Fig. 3, we can see that the conditions of the motion of a free electron within the crystal and the conditions of the motion of an electron from one bond to another are absolutely different. The motion from one orbit to another turns out to be much more difficult. In the same external field, the hole, as a rule, moves more slowly than the electron.

#### 1.1.3 Generation and recombination

The chaotic thermal motion is steadily breaking electron bonds between the atoms and generates free electrons and holes. Is it possible that finally, as a result of that process, all the electron bonds will be broken and the semiconductor will become a metal? No, it is not!

Moving chaotically in the crystal, the free electron and the hole may happen to be close to each other. The free electron will take its place on the free trajectory of the interatomic link and ... both the free electron and hole disappear simultaneously. This process is called *recombination* which, when translated from Latin, means "reunion." In a steady state condition, there is a dynamic equilibrium: the number of electrons and holes (electron-hole pairs) generated every second in the volume of the semiconductor on account of thermal generation is equal to the number of those annihilated on account of recombination. A certain equilibrium concentration of electrons and holes is established in the semiconductor at a given temperature.

In crystals whose properties we study, electrons and holes are always created in pairs and they always perish in pairs. Therefore the concentration of electrons  $n_i$  is equal to the concentration of holes  $p_i$  (The index "i" comes from the word "intrinsic"). Let us determine the temperature dependence of the equilibrium concentration of the free carriers  $n_i = p_i$ .

To do it, we must determine how many free carriers are formed in one unit of volume of the semiconductor per unit of time and how many of them perish during the process of recombination. In the case of equilibrium, these two values must be equal to each other. Equating them to each other, we will determine the equilibrium concentration of the carriers.

**Thermal generation.** We have already learned the main feature of the electron-hole pair generation under the action of thermal motion. It takes much more energy than the average energy kT.

Investigating various physical processes we often come across situations where to make a certain event take place it is necessary to expend a large "portion" of energy  $\Delta E$ , much greater than kT. That happens when we study the evaporation of water, or the decay of the nucleus; when we investigate the emission of the electrons by the cathode of the vacuum tube or the distribution of the density of gases in the atmosphere. In one of the main parts of physics, statistical physics, it is proven that the probability of such an event is always proportional to  $\exp(-\Delta E/kT)$ :

$$w \approx e^{-\frac{\Delta E}{kT}} \tag{1}$$

where e is a number equal to 2.7183... It is called the natural logarithmic base.

The values of the energies  $\Delta E = E_g$ , necessary to break the electron bonds in various semiconductors, are known to us. Consequently, knowing the temperature T, we can calculate by Eq. (1) the probability of forming an electron-hole pair in different materials. At room temperature (kT = 0.026 eV), for InSb ( $E_g = 0.17 \text{ eV}$ ), this probability is proportional to

$e^{-6.54} \approx 1.44 \cdot 10^{-3}$ . For Si  $(E_g = 1.1 \text{ eV})$ , the probability is proportional to  $e^{-42.3} \approx 4.23 \cdot 10^{-19}$ ; for GaAs  $(E_g = 1.4 \text{ eV})$ ,  $e^{-53.8} \approx 4.12 \cdot 10^{-24}$ .

Those examples illustrate the main feature of the exponential dependence: with the change of the index of the exponent, the value of the exponent changes a lot. The increase of  $\Delta E$  by approximately 1.27 times diminishes the probability of the formation of an electron-hole pair by approximately 100 000 times! (cf. the probabilities for Si and GaAs). We will note that a similar change of the probability of forming electrons and holes will occur in one and the same semiconductor if the temperature is changed. So to decrease the probability of forming an electron-hole pair in Si by 100 000 times, it is enough to cool the crystal of silicon, lowering the temperature from room temperature to  $-78^{\circ}$ C, i.e. to the temperature of dry ice, used to store ice-cream.

So, the number of electron-hole pairs  $K_1$  being formed every second in a unit of volume of a semiconductor is

$$K_1 = \alpha e^{-\frac{E_g}{kT}} \tag{2}$$

where  $\alpha$  is a coefficient of proportionality, different for different semiconductors.

On the other hand, due to recombination, a certain number of charge carriers  $K_2$  will disappear from the same unit of volume every second. So what does the number of recombining carriers depend on?

**Electron-hole recombination.** In order to recombine, the electron and hole must meet. What does the frequency of their meetings depend on? Let us mentally make the following experiment. We will watch some atom of the crystal lattice and mark the appearance of a hole in its vicinity. It is clear that the greater the number of holes per unit of volume of the semiconductor, the more frequently they appear there. The probability of the appearance of a hole is proportional to the concentration of holes  $p_i$ . For the same reason, the probability of the appearance of a free electron in the vicinity of that atom is proportional to the concentration of electrons  $n_i$ . We are interested in the probability of a simultaneous appearance of both the electron and the hole in the vicinity of the atom. This probability (i.e. the probability of their meeting and recombination) is proportional to the product of the concentrations of electrons and holes  $n_i \cdot p_i$ . Thus, the number of carriers recombining every second per unit of volume is the following:

$$K_2 = \beta \cdot n_i \cdot p_i \,. \tag{3}$$

The coefficient  $\beta$  as well as  $\alpha$  in Eq. (2), is different for different semiconductors.

Since  $n_i = p_i$ , then

$$K_2 = \beta \cdot n_i^2 = \beta \cdot p_i^2 \,. \tag{4}$$

Equating the number of the newly born pairs  $K_1$  to the number of the perishing pairs  $K_2$ , we obtain:

$$\alpha e^{-\frac{E_g}{kT}} = \beta \cdot n_i^2 = \beta \cdot p_i^2 \,. \tag{5}$$

Hence we obtain

$$n_i = p_i = \sqrt{\frac{\alpha}{\beta}} \cdot e^{-\frac{E_g}{2kT}} = (A \cdot B)^{1/2} \cdot e^{-\frac{E_g}{2kT}}.$$

(6)

Values A and B in Eq. (6) are measured in cm<sup>-3</sup>. They are known for all the semiconductors we will deal with. At room temperature these values are within the limits approximately from  $10^{17}$  to  $10^{19}$  cm<sup>-3</sup>. Knowing the values of A and B, it is easy to calculate by Eq. (6) the values of the concentration of intrinsic carriers in any semiconductor at any temperature.

**Intrinsic concentration.** Table 1 gives the values  $E_g$  and  $n_i$  for some semiconductors at room temperature (300 K).

|                                                  |                    |                   | 10010 1           |                |                 |     |                    |

|--------------------------------------------------|--------------------|-------------------|-------------------|----------------|-----------------|-----|--------------------|

| Semiconductor                                    | InSb               | Ge                | Si                | InP            | GaAs            | GaP | SiC                |

| $E_g$ , eV                                       | 0.17               | 0.72              | 1.1               | 1.3            | 1.4             | 2.3 | 2.4 - 3.2          |

| Intrinsic concentration $n_i$ , cm <sup>-3</sup> | $1.3\cdot 10^{16}$ | $2.4\cdot10^{13}$ | $1.1\cdot10^{10}$ | $5.7\cdot10^7$ | $1.4\cdot 10^7$ | 0.8 | $0.12 - 2.10^{-8}$ |

Table 1

We remember that every cubic centimetre of metal contains  $\sim 10^{22}$  conduction electrons. From Table 1, we can see that even in a semiconductor with a small value of  $E_g$  — InSb, the concentration of intrinsic electrons at room temperature is a million times smaller than that in a typical metal.

In Si, it is a trillion times (by a factor of  $10^{12}$ ) smaller. In GaAs, it is smaller by a factor of  $10^{15}$ . And in silicon carbide (SiC), it is smaller by a factor of  $10^{30}$ !

We can see from Eq. (6) that the concentration of the carriers, (and consequently the conductivity) grows abruptly with the rise of temperature. The values A and B, speaking generally, do not change much with the temperature. The main contribution into temperature dependence of the intrinsic concentration is made by an exponent. Table 2 gives the values of  $n_i$  at the temperature of 500 K for the same semiconductor materials:

| Table 2 | 2 |

|---------|---|

|---------|---|

| Semiconductor                                              | InSb | Ge                  | Si                | InP               | GaAs                | GaP            | SiC         |

|------------------------------------------------------------|------|---------------------|-------------------|-------------------|---------------------|----------------|-------------|

| Intrinsic concentration $n_i$ (cm <sup>-3</sup> ) at 500 K |      | $6.4 \cdot 10^{15}$ | $5.6\cdot10^{13}$ | $1.4\cdot10^{12}$ | $7.2 \cdot 10^{11}$ | $4.4\cdot10^7$ | $\sim 10^2$ |

We can see that the greater  $E_g$  is, the more abruptly the temperature of the intrinsic concentration grows. If the temperature increases 1.7-fold, the intrinsic concentration in InSb increases about 3.7-fold; in Si, about 5 000-fold; and in SiC, by a factor of  $10^{10}$ !

An abrupt growth of conductivity with the rise of temperature is one of the most characteristic properties of intrinsic semiconductors.

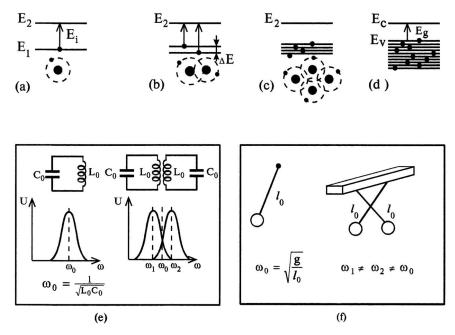

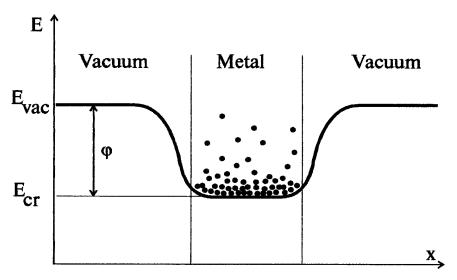

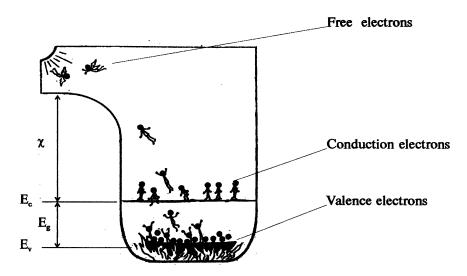

The simplest band diagrams. There is a very simple and easy method, giving a qualitative description of what we now know about the processes of generation and recombination. It is the so-called *method of band diagrams*. That method or "language" of band diagrams is widely used when analyzing semiconductor devices. It enables describing most complicated situations in a distinct and concise form and is sometimes quite indispensable. In this section, we use the band diagram language to render the most simple notions.

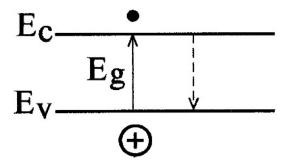

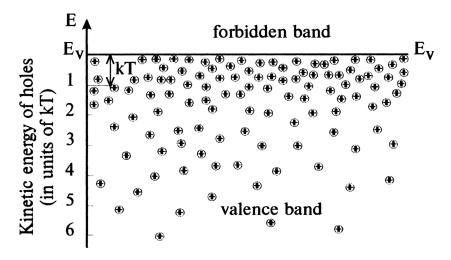

In order to have the electron and hole appear in a semiconductor, it is necessary to expend the energy  $E_g$ . We will depict the process of the birth of this pair schematically (Fig. 4). Let us assume that while the electron is in the orbit connecting the silicon atoms, it possesses the energy  $E_v$ . (The index "v" denotes valence, for we deal here with valence electrons.)

In order to get a conduction electron and hole (to form an electron-hole pair), it is necessary to expend energy, or, in other words, to overcome an energy barrier whose height is  $E_g$ . The energy  $E_g$  can be obtained from thermal fluctuations of the lattice or else from a rather energetic quantum of light-photon. In case the energy barrier has been overcome, the electron gets

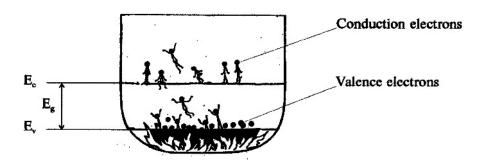

Fig. 4. Band diagram illustrating generation and recombination processes in an intrinsic semiconductor.

to the level  $E_c$ . (The index "c" denotes conductivity). So there appears a conduction electron (black dot) and a hole (white circle with the mark "+"). The band diagram makes the notion of the energy barrier distinct and obvious: it is a portion of energy, necessary for some process to take place.

The process of the recombination of electron and hole in the intrinsic semiconductor can also be easily imagined by means of a band diagram. In Fig. 4, this process is indicated by a dotted arrow. The same amount of energy  $E_g$  that was spent to form an electron-hole pair is given off during the process of recombination. Sometimes recombination is followed by the birth of a quantum of light — the photon with the energy  $E_g$ . But quite often the electron and hole recombine without giving birth to any photon. Then the energy  $E_g$  is transferred to the lattice, heating it up. On our request, the artist represented the band diagram in Fig. 5 even more vividly. Only very few

Fig. 5. Vivid illustration of the band diagram in Fig. 4.

electrons under the action of thermal motion manage to break through the fetters of the electric field which keep the valence electrons in interatomic orbits (at the  $E_v$  level). Those lucky ones become conduction electrons. Their concentration is proportional to  $\exp(-E_g/kT)$ . However, they should also be vigilant. They may easily get into a hole (recombination) and end up on the  $E_v$  level.

#### 1.2 Impurity Semiconductors

There are no ideal things in nature. And there are no substances containing atoms only of one definite kind. Any real crystal, including the semiconductor crystal, always contains certain foreign impurities. Impurities are found in natural raw materials from which semiconductors are synthesized. Besides, there are impurities in the walls of the furnaces and installations where the synthesis and purification of semiconductors take place and in the atmosphere as well.

One cubic centimetre of various crystals contains  $\sim 10^{22}$  atoms. A substance is usually called pure if it contains one foreign atom per 1000 intrinsic atoms (i.e. the impurity concentration is  $\sim 0.1\%$ ). From the chemical point of view, the substance will be absolutely pure if it contains one foreign atom per 100 000 intrinsic atoms. Nevertheless it means that every cubic centimetre of the substance will contain  $\sim 10^{17}$  foreign atoms. And now let us imagine that there is an impurity in the semiconductor which is able to release quite easily a free electron or form a hole. (Later on, we will see that very many impurities possess this property). Then germanium, absolutely pure from the chemical point of view, (the concentration of impurity will be only 0.001%) will at room temperature contain such a number of impurity electrons which will exceed the number of intrinsic electrons by a factor of 4000. In silicon, the number of impurity electrons will be 10 000 000 times greater than that of the intrinsic ones: in gallium phosphide, it will be  $10^{17}$  times greater!

That is why in actual practice one seldom deals with intrinsic semiconductor materials. The great majority of semiconductor materials contain a certain controlled amount of impurities which provide the necessary value of the conductivity.

Let us see how the density of free carriers in a crystal is affected by impurities. We will begin with the simplest example.

### 1.2.1 Donor impurity

Let us assume that an intrinsic atom has somehow got into a silicon crystal and occupied a place in one of the sites of the crystal lattice, substituting its lawful host — the silicon atom. Now let us look at Fig. 6. The atom of As takes the place of the silicon atom in site 15. The silicon atom has four valence electrons; the arsenic atoms have five valence electrons. The four valence electrons of arsenic atoms make bonds with the neighbouring silicon atoms (atoms 9, 14, 16 and 21). Now what about the fifth electron?... The fifth electron will be held by the As atom, but much more weakly than the other four electrons, which are very tightly bound in their electron orbit, determined by the structure of the silicon crystal. The energy  $\Delta E$ , necessary to break the bond of the fifth electron with the arsenic atom and to transform it into a free electron, is much smaller than the energy  $E_g$  necessary to break the bond between the silicon atoms and form an electron-hole pair.

Fig. 6. The donor atom (As) in the silicon lattice.

The impurity whose atoms give away their electrons easily is called a *donor impurity*. The Latin word "donare" from which the word "donor" comes, means "to endow," "to give."

Let  $N_d$  atoms of a donor, say of arsenic, be introduced into every cubic centimetre of a crystal. Now let us first consider the simplest situation — the temperature of the crystal is T=0 K. It is clear that in this case the crystal remains an ideal dielectric: though it takes a very small amount of energy to break away the fifth electron from the arsenic atom — the temperature being equal to absolute zero — there is no energy of thermal oscillations whatsoever.

If the temperature of the crystal is T > 0, then the equilibrium density of the impurity electrons  $n_d$  is determined by the expression, analogical to Eq. (6)

$$n_d = (A \cdot N_d)^{1/2} e^{-\frac{\Delta E}{kT}} \tag{7}$$

Instead of a large value  $E_g$ , we have in the exponent a much smaller value  $\Delta E$ . The ionization energy  $\Delta E$  (which is sometimes called the activation energy of impurity) of arsenic in silicon is very small. It is equal to 0.05 eV, which is twenty times smaller than the energy  $E_g$  necessary to create an electron-hole pair in silicon. According to Eq. (7) (and according to common sense), it means that the ionization of the arsenic atoms, i.e. the detachment of the extra fifth electron, will take place at a temperature much lower than that of the generation of the intrinsic electrons and holes.

Let us now consider silicon into which a donor impurity (As) has been introduced. The density of the impurity atoms is  $N_d = 10^{15} \text{ cm}^{-3}$ .

This implies that there are 10 000 000 Si atoms per single As atom. From a chemist's point of view, there is no arsenic in the silicon at all. But the value  $N_d \approx 10^{15} \ {\rm cm}^{-3}$  is very typical for many cases of practical importance.

In silicon,  $A \approx B \approx 10^{19} \text{ cm}^{-3}$ . Now by Eqs. (6) and (7), it is quite easy to calculate that with the temperature at 10 K, the density of the impurity electrons would make  $n_d \approx 2.5 \cdot 10^4 \text{ cm}^{-3}$ , while the density of the intrinsic electrons would be so small that even if a crystal were as big as the galaxy, there would not be a single intrinsic carrier in it.

At a temperature of 50 K, the value  $n_d$  is equal to  $\sim 3 \cdot 10^{14}$  cm<sup>-3</sup>, while the concentration of the intrinsic electrons is still practically equal to zero in any real crystal. Note that at this temperature, about one-third of the impurity atoms have been ionized.

As for room temperature (300 K), it would be wrong to calculate the concentration of the impurity electrons by means of Eq. (7) since it is not

exact but just an approximation. It can be used only in those cases where the calculated value  $n_d$  is much smaller than the concentration of the impurity atoms  $N_d$ , i.e. when  $kT \ll \Delta E$ .

But if the temperature is so high that  $kT \sim \Delta E$  (or moreover if  $kT > \Delta E$ ), then all of the impurity atoms prove to be ionized and the concentration of the impurity electrons is just equal to  $N_d$ . This phenomenon is called the "impurity saturation (exhaustion)" — the term seems quite reasonable. When the temperature is high enough, all the impurity atoms give away "extra" electrons and the source of the electrons is "exhausted." No further rise in the temperature of the crystal will increase the concentration of the impurity electrons.

In Si, room temperature (300 K) corresponds to the impurity saturation region. So in our example when T=300 K,  $n_d=N_d=10^{15}$  cm<sup>-3</sup>. The concentration of the intrinsic electrons  $n_i$  at 300 K is equal to only  $\sim 10^{10}$  cm<sup>-3</sup> (see Table 1), which is 100 000 times smaller. And only at the temperature of  $\sim 600$  K (300°C) will the intrinsic concentration in silicon be equal to  $\sim 10^{15}$  cm<sup>-3</sup> and become equal to the concentration of the impurity.

When the concentration of the impurity  $N_d \cong 10^{18} \ {\rm cm^{-3}}$ , the silicon crystal should be heated up to the temperature somewhat more than 1000 K (700°C) so that the intrinsic concentration might be equal to the impurity concentration.

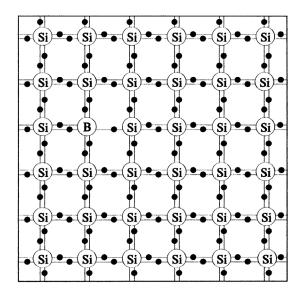

## 1.2.2 Acceptor impurity

Figure 7 shows a crystal lattice of silicon in which one of the sites is occupied by the boron impurity atom. Boron (B) is trivalent — there are three electrons on its outer electron shell. It is one electron short of making a complete bond with the neighboring silicon atoms.

Compare the picture of the electron bonds of the B atom in Fig. 7 with the configuration of the electron bonds around atom 19 in Fig. 3. The situations are quite similar, aren't they? Both the silicon atom 19 in Fig. 3 and the B atom in Fig. 7 are short of one electron. But there is also a great difference between them. All the silicon atoms are quite identical, and the empty link, the hole, which now belongs to atom 19 may at any moment approach atom 14, then atom 9 and so on.

It does not take any energy for the hole to travel in the crystal. But a boron atom is a stranger in the silicon lattice. To make the electron of the neighboring silicon atom to go over to boron, it is necessary to expend energy

Fig. 7. The acceptor atom (B) in the silicon lattice.

$\Delta E$ . This energy, the activation energy, is not large (for B atoms in Si, it is only 0.045 eV), and yet it is not zero, as in the case of a hole in Fig. 3. No hole will be formed in the crystal until the "energy barrier"  $\Delta E$  is overcome, no matter how small it is.

Let us assume that either the lattice vibrations or a quantum of light have supplied the necessary energy, and that the electron from the neighboring Si atom has come over to boron. Now the situation will be identical to that shown in Fig. 3. There is an empty link in the lattice, i.e. a hole — a free carrier of positive charge. So, acceptor impurities create holes — free carriers in a semiconductor crystal. If the temperature of the crystals is T > 0, then the equilibrium density of the impurity holes  $p_a$  can be found from the expression analogous to Eq. (7).

$$p_a = (B \cdot N_a)^{1/2} e^{-\frac{\Delta E}{kT}} \tag{8}$$

The value B here is the same as in Eq. (6).  $N_a$  is the density of the acceptors.

The appearance of a hole in an impurity semiconductor is not accompanied by the appearance of a conduction electron, which is clearly seen from Fig. 7.

Equation (8), like Eq. (7), is rather approximate. It can be used only if the value  $p_a$ , calculated by it, is much smaller than the concentration of the impurity atoms  $N_a$ , i.e. when  $kT \ll \Delta E$ . If  $kT \sim \Delta E$ , or moreover, if  $kT > \Delta E$ , then all the boron atoms will take away electrons from the neighbouring silicon atoms, and the concentration of holes  $p_a$  will be equal to the concentration of the introduced impurity  $N_a$ .

### 1.2.3 The temperature dependence of the carrier concentration

A semiconductor into which some donor impurity has been introduced is called an electronic semiconductor, or a semiconductor of n-type. The letter "n" comes from the word "negative", showing that the semiconductor contains many negatively charged particles — electrons.

A semiconductor into which some acceptor impurity has been introduced is called a hole semiconductor, or a semiconductor of p-type. The letter "p" comes from the word "positive", showing that the semiconductor contains positively charged particles — holes.

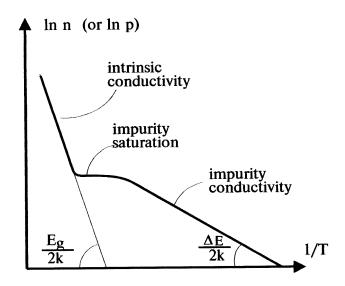

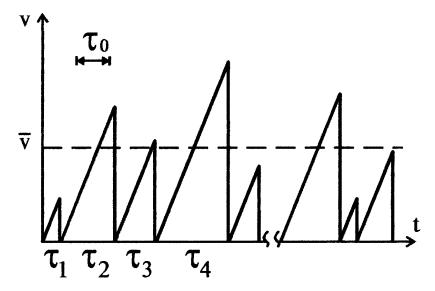

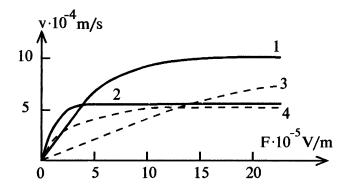

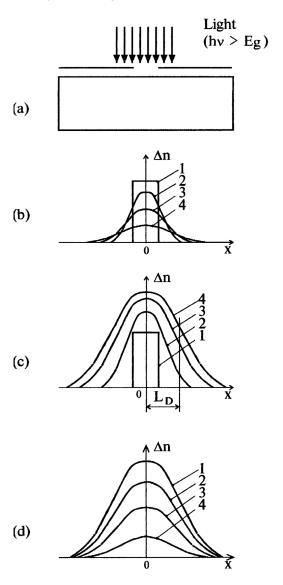

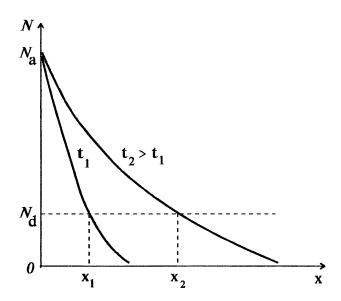

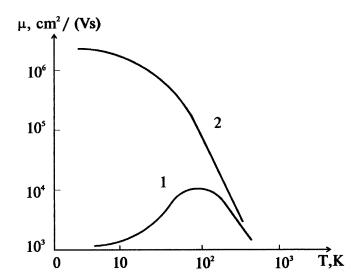

Look at Fig. 8. The curve, shown there, gives a short summary of what we have learnt about the properties of both intrinsic and impurity semiconductors. The curve represents a typical temperature dependence of the equilibrium

Fig. 8. The typical temperature dependence of carrier concentration.

density of free carriers in a semiconductor. The value of the natural logarithm of the concentration of electrons  $\ln n$  (if the n-type semiconductor is meant) or  $\ln p$  (if the p-type semiconductor is meant) is plotted on the y-coordinate. Note that it is not the value of T, but its inverse value 1/T that is plotted on the abscissa.

And now we will discuss the dependence shown in Fig. 8. We begin from the right, from the low temperature region, where the value 1/T will be great, and we will advance on the abscissa from the right to the left. As we have seen, at low temperatures the carrier (electron or hole) density in a semiconductor is determined by the density of impurity centres. The carrier density increases with the rise of temperature, and this section of the curve is determined by Eq. (7) for the electron or by Eq. (8) for the hole semiconductor. At a certain temperature this dependence is saturated. It is the impurity saturation region. All the impurity atoms have already been ionized and the carrier concentration is equal to the donor concentration (for the n-type semiconductor) or to the acceptor concentration (for the p-type semiconductor), but the intrinsic carrier density is still much smaller than that of the impurity. Finally, in the region of a still higher temperature, there is an abrupt increase of the density with a further rise of temperature. It is the region of intrinsic conductivity where the n(T) dependence is expressed by Eq. (6).

And now a few words about the choice of the coordinates in Fig. 8. Let us take the logarithm of Eq. (6)

$$\ln n_i = \frac{1}{2} \ln(A \cdot B) - \frac{E_s}{2k} \frac{1}{T} \tag{9}$$

and we will denote x=1/T;  $y=\ln n_i$ ;  $a=\ln(AB)$ , b=Eg/2k, Eq. (9) will look familiar: y=a-bx - the equation of a straight line. So, if we plot  $\ln n_i$  on the y-coordinate, and 1/T on the abscissa until Eq. (6) is valid, then the dependence  $\ln n_i(1/T)$  must be a straight line. And, what is especially important, the slope of the curve of this straight line b=Eg/2k is directly proportional to the important parameter of the semiconductor - Eg. In the early works on semiconductors this way of defining Eg was used very often. It is sometimes used nowadays too, when studying the properties of new semiconductors.

If the same operation of taking the logarithm is repeated with Eq. (7) or (8), it is easy to see that the slope of the straight line  $\ln n(1/T)$  is proportional to the value  $\Delta E$ .

#### 1.2.4 Minority carriers

And now we will discuss a very important question regarding the concentration of holes in an electronic semiconductor and the concentration of electrons in a hole semiconductor.

First of all it should be mentioned that when the donor atom gets ionized and yields an electron, no hole is formed. The arsenic atom in Si lattice, for instance, having yielded the fifth valence electron remains bound with the adjacent atoms of silicon by four "valid" bonds. There is no empty place where electrons from the adjacent orbit could be displaced. Therefore no hole is formed.

On the face of it, it might seem that the electronic semiconductor must then have as many holes as the absolutely pure intrinsic semiconductor. But that view would be wrong. It is true that at a given temperature T the number of broken electron bonds and electron-hole pairs, appearing every second in an electronic semiconductor, is exactly equal to those in an intrinsic semiconductor. But the holes perish much more often, because there are more free electrons in the electronic semiconductor than in the intrinsic one. That means that a hole will meet with an electron much more often and each time it will result in a recombination and the disappearance of the hole. A a result of it, there are fewer holes in the n-type semiconductor than in an intrinsic semiconductor. There is a very simple equation connecting the equilibrium density of holes p and the electrons n in a semiconductor

$$p \cdot n = n_i^2(T) \,. \tag{10}$$

The greater the number of electrons, the smaller the number of holes and vice versa.

The quantity  $n_i$  in Eq. (10) represents the value of the intrinsic carrier density at a given temperature T and is defined by Eq. (6).

By using Eqs. (10) and (6) it is easy to calculate that in n-type silicon, say, at room temperature, and with the electronic density of  $10^{15}$  cm<sup>-3</sup>, the hole density will be  $\sim 10^5$  cm<sup>-3</sup>, i.e. ten billion times smaller than that of the electrons!

So it seems quite natural that the electrons in the n-type semiconductor are called the majority carriers while the holes are called the minority carriers. In the semiconductor doped with acceptors; in the hole semiconductor, it is just the opposite — the holes will be the majority carriers, while the electrons will be the minority carriers.

The appearance of a hole in a *p*-type semiconductor is not accompanied by the appearance of a conduction electron, which is clearly seen in Fig. 7. The electrons in a hole semiconductor appear only on account of the generation of electron-hole pairs in exactly the same way as in the intrinsic semiconductor. But they perish much sooner than in the intrinsic semiconductor because the

possibility of a collision with a hole and recombination here is much higher.

So, what happens to the electrons in a hole semiconductor is absolutely the same as to holes in the n-type semiconductor. No wonder that Eq. (10) is valid for the p-type semiconductors, as well. But now there will be more holes than electrons. Say, if in the p-type silicon the concentration of major carriers, i.e. holes, makes  $10^{15}$  cm<sup>-3</sup>, the concentration of minor carriers, i.e. electrons, will be  $\sim 10^5$  cm<sup>-3</sup>.

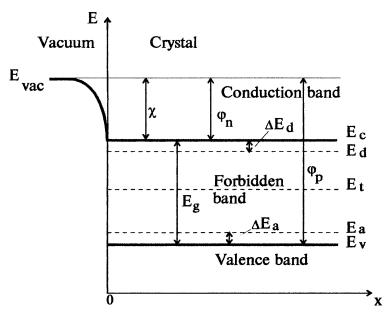

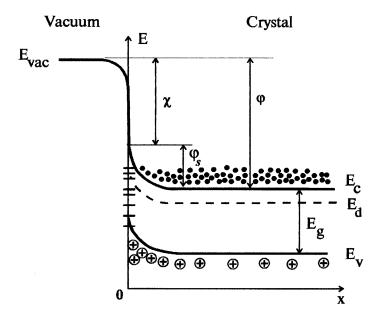

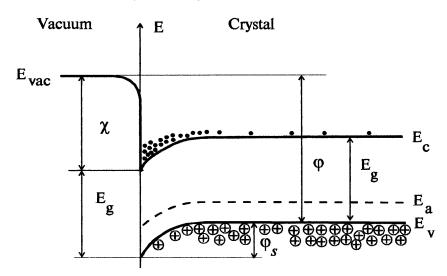

### 1.2.5 Band diagrams

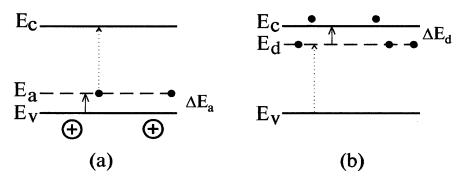

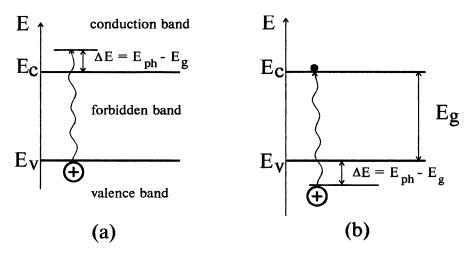

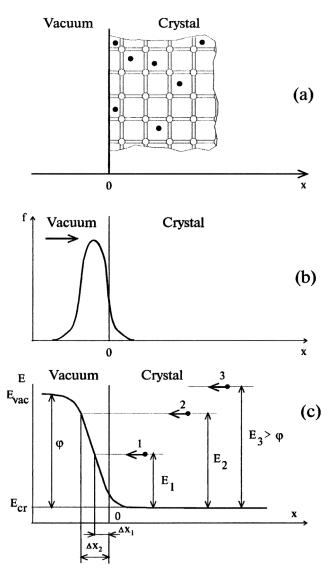

In the previous section we discussed the main characteristics of impurities whose activation energy  $\Delta E$  is not large, and makes up but a small portion of the energy  $E_g$  of generating an electron-hole pair. Such impurities are called shallow. Figure 9 indicates band diagrams, illustrating the behaviour of shallow impurities. Figure 9(a) shows the processes in a crystal which contains shallow acceptor centres. The  $E_a$  energy level differs from the  $E_v$  energy level by the value of the acceptor level activation energy  $\Delta E_a$ .

With T = 0, the  $E_a$  level is empty, with no electrons there. Recall, "this energy, the activation energy is not large (for the boron atoms in Si, it

Fig. 9. Appearance of holes in the crystal with shallow acceptor levels (a); Appearance of electrons in the crystal with shallow donor levels (b).

is only 0.045 eV), and yet it is not zero. No hole will be formed in the crystal until the "energy barrier"  $\Delta E$  has been overcome, no matter how small it is ..." With the temperature T>0, though low enough such that  $kT\ll\Delta E_a$ , holes will appear in the crystal. Their concentration is defined by Eq. (8). But Eq. (8) also defines the concentration of electrons at the  $E_a$  level at the temperature T. Indeed, holes in the p-type crystal are formed just because electrons from the  $E_v$  level are captured by the acceptor level  $E_a$ . The number of electrons captured by the acceptor level is equal to the number of mobile holes which appear in the crystal.

The process of the formation of holes and of capturing the electrons by the acceptor centres is shown in Fig. 9(a) by a solid arrow. The acceptor atom which has captured the electron is charged negatively. This bound electron, unable to transfer the current, is held by the acceptor atom very tightly. It is seen from Fig. 9(a) that to release the electron, captured at the acceptor level, it is necessary to exert energy  $E = E_c - E_a = /E_g - \Delta E_a/$ . (The process of releasing the electron — its transfer to the  $E_c$  level, is shown at Fig. 9(a) by a dotted arrow (cf. Fig. 4)).

If  $\Delta E_a \ll E_g$  (shallow level), then the energy necessary to release the electron, captured by the acceptor, is almost as large as the energy  $E_g$ .

When the value kT is of the same order as the value  $\Delta E_a$ , or even greater, all the acceptor centres will be taken by electrons, and the hole concentration will be equal to  $N_a$  — the concentration of the acceptor atoms introduced into the crystal (the impurity exhaustion).

Figure 9(b) shows a band diagram of an electronic semiconductor containing the donor shallow impurity. With T=0, the concentration of conduction electrons at the  $E_c$  level is equal to zero. The energy level  $E_d$ , corresponding to the donor centre, is filled up with electrons. Then the donor atoms which keep the electrons are neutral. When T is not too high, the concentration of electrons at the  $E_c$  level is defined by Eq. (7). The donor atoms which have given their electrons to the  $E_c$  level are charged positively. The concentration of those positively charged donor centres is, naturally, also defined by Eq. 7.

With  $kT \geq \Delta E_d$ , the concentration of free electrons at the  $E_c$  level and the concentration of the positively charged donor centres are equal to  $N_d$  (the donor exhaustion).

The positively charged donor centre can capture an electron from the  $E_v$  level. Then there appears a hole in the crystal. But in order to transfer an

electron from the  $E_v$  level to the donor level  $E_d$  and thus create a hole in the crystal (this process is shown in Fig. 9(b) by a dotted arrow), it is necessary to overcome an energy barrier whose height is  $E_q - \Delta E_d \approx E_q$ .

Pay attention to a very important feature, which is clearly seen in the diagrams: if the electrons are not affected by any exterior disturbances, they are at the lowest of the energy levels.

Indeed, in the intrinsic semiconductor when T=0 and there is no illumination, as we know there are neither electrons nor holes there. In the language of band diagrams (Fig. 4) that means that all electrons are at the lowest of all the possible energy levels, at the level  $E_v$ .

In a semiconductor containing the acceptor centres with T=0 and without any illumination, all the electrons are also on the level  $E_v$ . The levels  $E_a$  and  $E_c$  are empty [Fig. 9(a)].

In the semiconductor containing donors [Fig. 9(b)], with T = 0, electrons are on the level  $E_d$ . But why not on the level  $E_v$ ?

The thing is that the electrons tend to occupy the lowest possible energy level. In the semiconductor crystal containing donors, with T=0, the level  $E_v$  is wholly filled with electrons. There are no vacant places there. And the electrons occupy the lowest possible level — the  $E_d$  level. Mind what that means in the physical sense. The level  $E_v$  corresponds to the energy of electrons binding the silicon atoms to each other. With T=0, all the electrons are in their orbits (Fig. 2) and there are no vacant places (holes) which the electrons from the donor level  $E_d$  might have occupied.

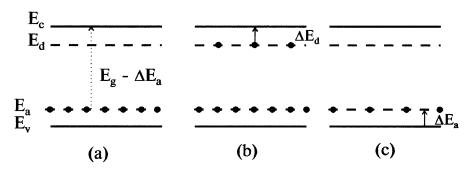

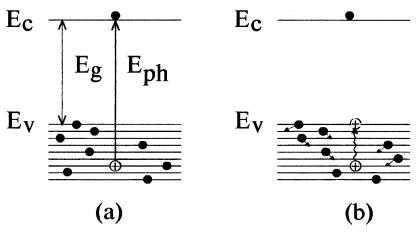

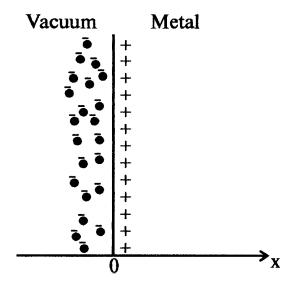

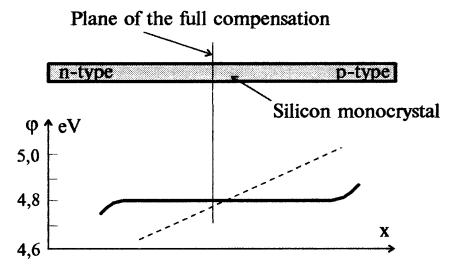

**Compensation.** Having learnt a few phrases in the language of the band diagram, we can solve a problem in a matter of seconds, in a distinct and memorable form. To get that answer in a traditional way, one should use a rather subtle physical reasoning.

The problem is formulated as follows: let us assume that the same amount of the donor and acceptor shallow impurities are simultaneously introduced into a semiconductor. For instance, the same quantity of arsenic and boron are introduced into silicon. What will happen? The natural answer is that there will be a great concentration of free carriers of both signs — electrons and holes.

But that answer is absolutely wrong. The right answer is that there will neither be impurity electrons nor impurity holes in the semiconductor, the latter behaving as an intrinsic semiconductor. Look at Fig. 10(a). All the electrons from the donor level  $E_d$  moved over to the lowest initially vacant

acceptor level  $E_a$ . Now, in order to create a free electron in the crystal, it is necessary to spend the energy  $E_g - \Delta E_a$ , which is almost as large as the energy  $E_q$ , necessary to create an electron-hole pair in an intrinsic semiconductor. It is hardly possible for the hole to appear in the crystal: all the vacant places on the acceptor level have been filled up by the electrons from the donor level  $E_d$ . There are no places on the acceptor level for the electrons from the  $E_v$  level. Since there might appear a hole in the crystal, it is necessary either to transfer an electron from the  $E_v$  level directly to the  $E_c$  level (which will require the energy  $E_q$ ), or to vacate a place on the  $E_a$  level. To do it, it is necessary to transfer the electron from the  $E_a$  level to the  $E_c$  level (the energy needed for  $E_q - \Delta E_q$  is almost as large as  $E_q$ ). It is enough to cast a look at Fig. 10(a) in order to see that the semiconductor, into which the donor and acceptor shallow impurities were introduced in the same concentration will behave almost in the same way as the intrinsic semiconductor. This phenomenon is called *compensation*. Introduction of the acceptor compensates for the action of the donor impurity and vice versa.

Fig. 10. Compensation. (a) Full compensation. The donor concentration  $N_d$  is equal to the acceptor concentration  $N_a$ . (b), (c) Partial compensation:  $N_d > N_a$  (b);  $N_d < N_a$  (c).

To what physical picture does the energy diagram in Fig. 10(a) correspond? Let us reason it out. Atoms of the donor impurity introduced into the crystal will easily give away their redundant electrons which will become free. Atoms of the acceptor impurity will capture electrons from their nearest lattice neighbours and will form an adequate number of holes. The impurity electrons and holes will begin wandering chaotically about the crystal and sooner or later will meet and recombine. In accordance with the conditions of the problem under consideration, the number of electrons which can easily be released is

exactly the same as the number of holes (since the concentration of shallow donors is equal to that of the acceptors). After the impurity electrons and holes have met, recombined and disappeared, there will be no more atoms in the crystal which might easily generate an electron or hole.

Indeed, if we consider the example with the silicon into which arsenic and boron were introduced, we will see that for each arsenic atom there will be only four valence electrons left, held almost as securely as the four valence electrons held by the silicon atom. The same can be said of the boron atom. On gaining the forth electron, the boron atom formed bonds with the neighboring Si atoms as solid as those between the silicon atoms. As a result of that, in order to generate a conduction electron or hole, it is now necessary to spend an amount of energy almost as large as that spent on generating an electron-hole pair in the intrinsic silicon.

And what will happen if the concentrations of the donor and acceptor impurities are not equal? Figure 10(b) and (c) allows us to answer that question.

Figure 10(b) refers to the case when the amount of the donor impurity is greater than that of the acceptor impurity, and the donor impurity is but partially compensated. The acceptor level is "rendered inoperative" (no impurity holes can be formed). There are still electrons left at the donor level  $E_d$ . Their concentration must be equal to  $N_d - N_a$ . The semiconductor will behave like that of n-type, whose donor concentration is equal to  $N_d - N_a$ . Figure 10(c) illustrates the case when  $N_a > N_d$ . The donor level is absolutely empty, and there are still vacant places at the acceptor level. Their concentration is  $N_a - N_d$ , the semiconductor behaving as a semiconductor of p-type with the acceptor concentration  $N_a - N_d$ .

Energy diagrams will help us understand the problems of generation, recombination and the movement of free carriers which will be considered in the next chapter. But the full meaning of the diagrams will become clear only in the second part of the book, where we will study the energy barriers, which are formed on the boundaries between the semiconductor and the surrounding medium or on the border between the semiconductors of n- and p-type.

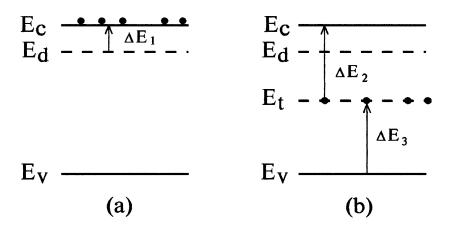

# 1.3 Deep Levels

There is a long list of impurities for any semiconductor which is commonly used, such as silicon, germanium, gallium arsenide, indium phosphide, etc. For silicon, for instance, this list contains several dozen names. It includes such familiar substances as arsenic, boron, phosphorus, aluminum, silver, copper,

cadmium, cobalt, gold, iron, oxygen, mercury, platinum, molibden, nickel, palladium, sulphur, selenium, tungsten, zinc and many other elements. Each of those elements is characterised, as an impurity in silicon, by its activation energy  $\Delta E$ , the values of those energies lying in the range from 0.05 eV (shallow donors and acceptors) up to 0.8-0.9 eV. The latter values, characteristic of the "deepest" impurities, are quite comparable to the energy  $E_g$  in silicon (1.1 eV).

One might think that the "deeper" the impurity (i.e. the greater  $\Delta E$ ), the smaller the role it has to play. And really, it is clear from Eqs. (7) and (8) that with the increase of  $\Delta E$  the density of free electrons (or holes) falls very fast exponentially. Equations (7) and (8) are valid for any value of  $\Delta E$ . But the conclusion that the "deep" impurities can be neglected would be quite wrong. Deep impurities in semiconductors play three very important roles: they act as "compensators", centres of generation and centres of recombination. We will consider each of these roles in turn.

# 1.3.1 Compensation by deep levels

Let us imagine that we want to obtain a semiconductor, say GaAs, with a very high resistivity. Specialists manufacturing the semiconductor devices are frequently facing such problems. Films or plates whose resistivity is very high are often used as a substrate to which very thin layers of the same semiconductor containing different doping impurities are applied.

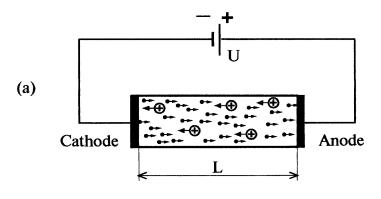

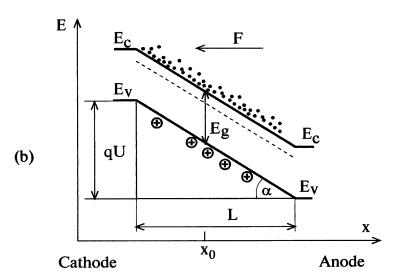

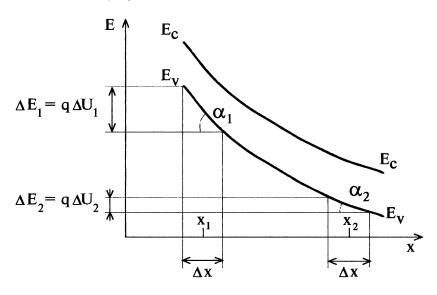

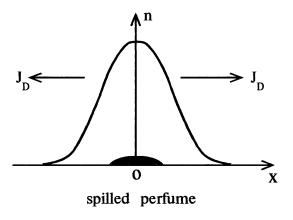

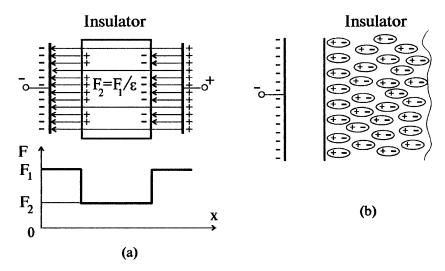

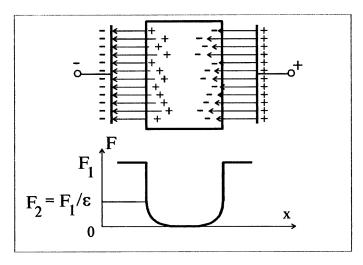

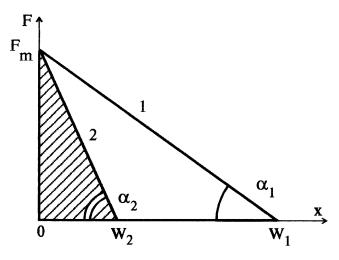

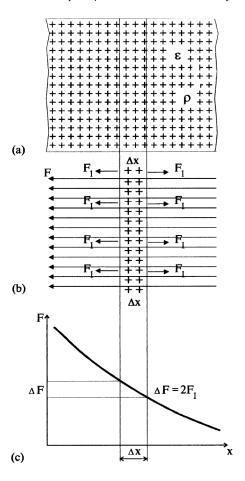

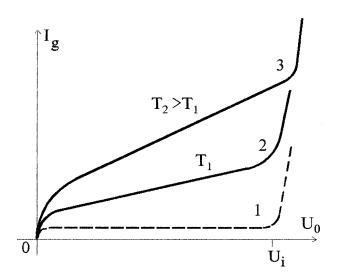

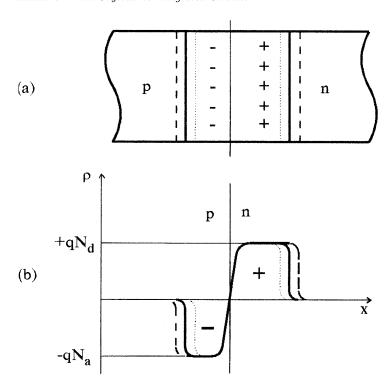

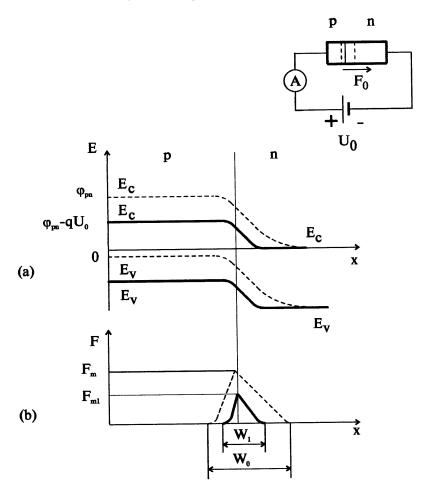

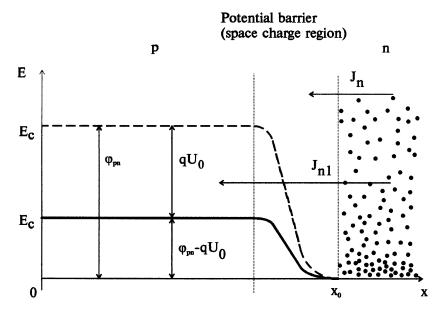

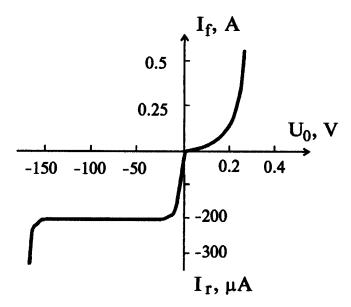

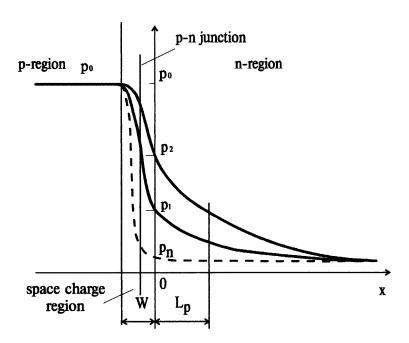

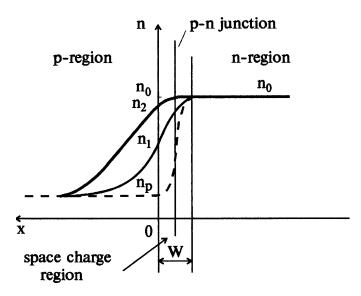

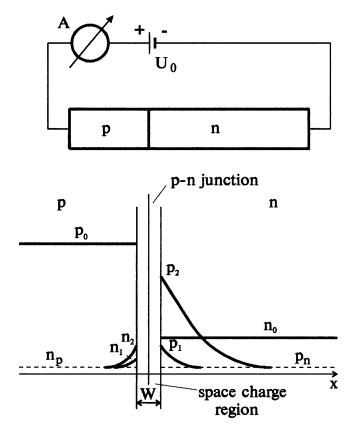

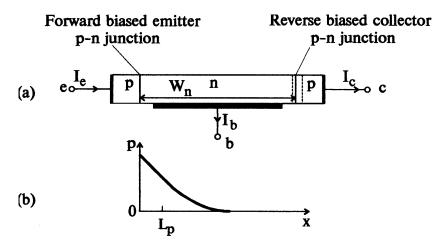

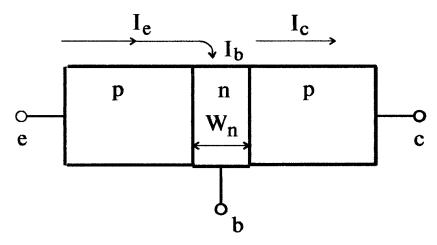

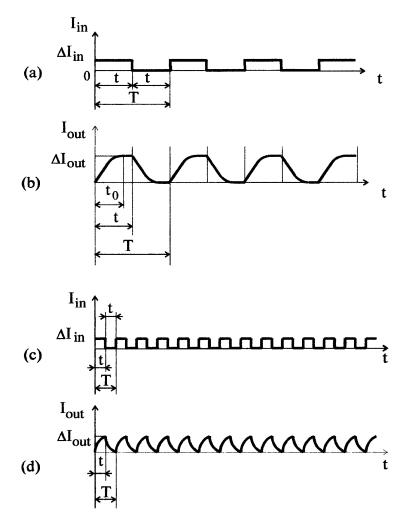

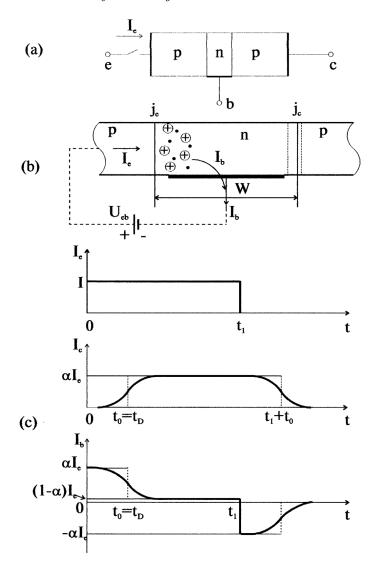

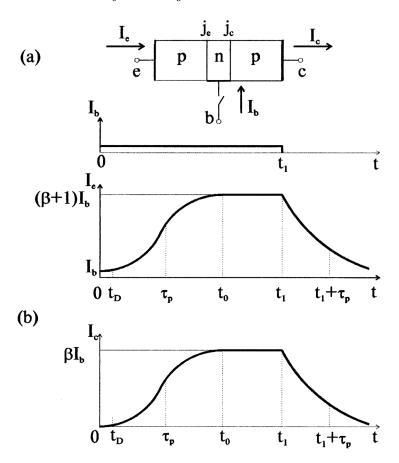

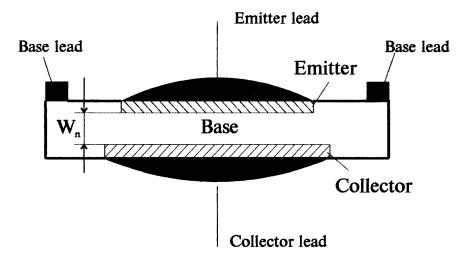

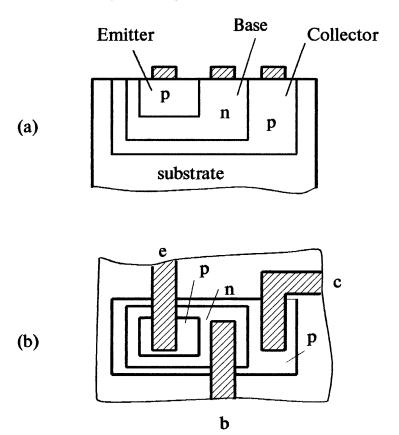

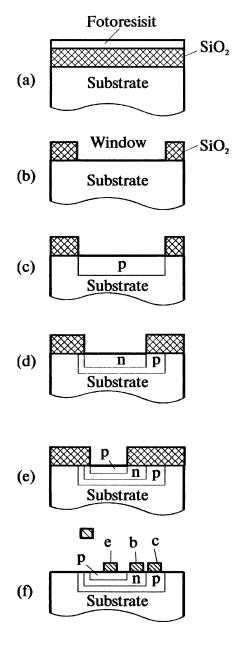

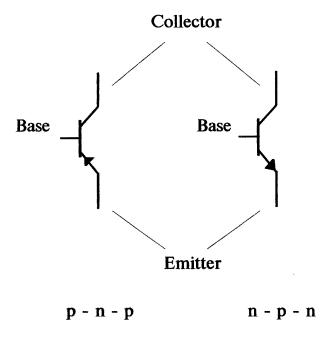

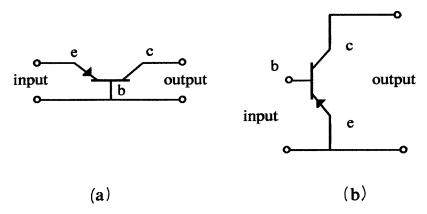

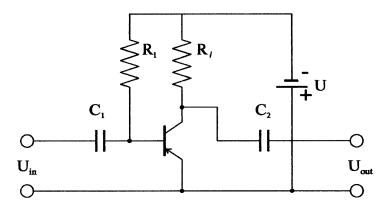

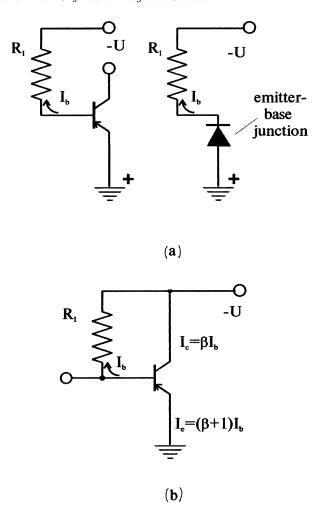

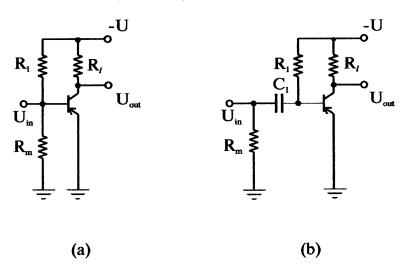

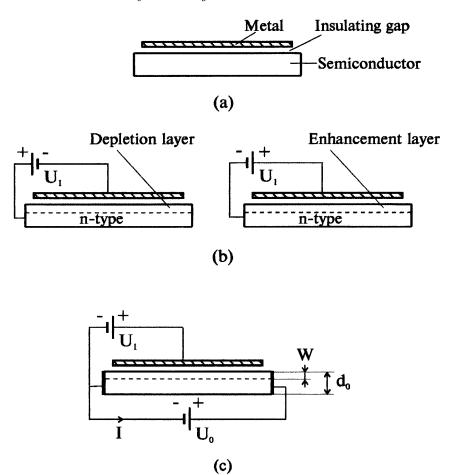

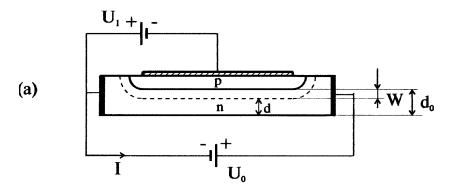

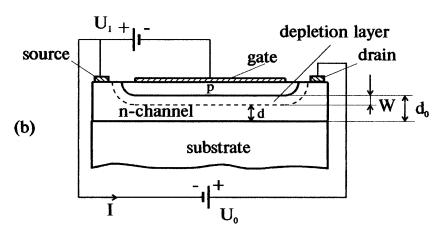

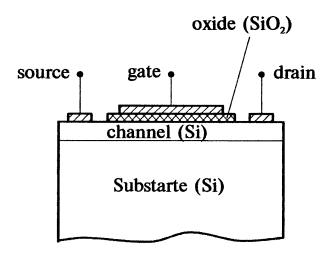

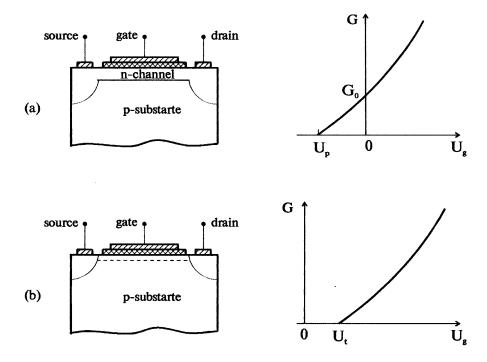

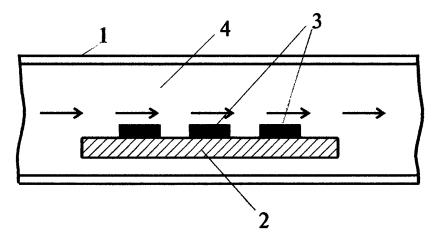

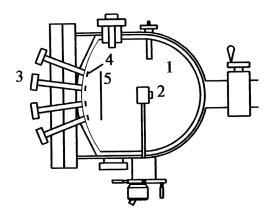

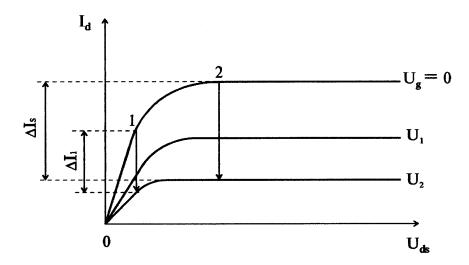

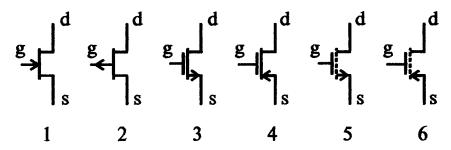

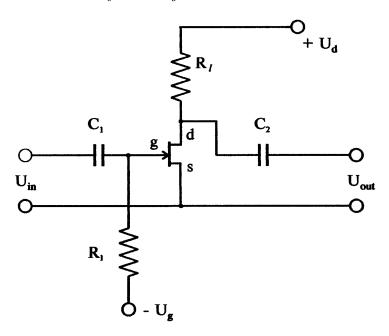

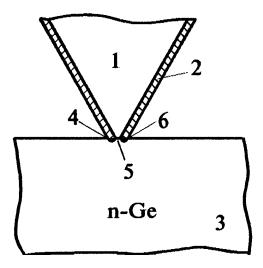

The intrinsic semiconductor has the highest resistivity: its number of free carriers being the smallest. But what we have already learned about the impurities in semiconductors is quite enough to make us realize how difficult it is to obtain intrinsic semiconductors. Even the smallest shallow impurity density makes the density of electrons and holes increase by thousands, millions and even billions of times.